We know that SERDES has strict phase noise performance requirements for the reference clock. In general, SERDES vendors will specify the phase noise of the reference clock based on the PLL and CDR architecture characteristics and performance data used by the SERDES. This requirement is usually based on not reducing its SERDES performance and is generally more stringent. So, can you not violate it at all? As a supplier, you always want a better reference clock, so the system has the largest margin. But as a user, I always want to use a cheap reference clock to meet the needs and have a certain margin. This requires a certain balance in engineering practice, you need to have a very clear understanding of system specifications, SERDES performance.

For example, the phase noise requirements of the CPLL of the XILINX 7 series SERDES for the reference clock are as follows:

Ref Clock Freq (MHz)

Phase Noise at Offset Frequency? (DBc / Hz)

10KHz

100KHz

1MHz

100

-126

-132

-136

125

-123

-131

-135

156.25

-121

-129

-133

250

-119

-126

-132

312.5

-116

-124

-131

625

-110

-119

-127

The user design needs to run the XAUI protocol, since the XAUI receiver's CDR jitter tolerance inflection point is about 1.87MHz. Therefore, the phase noise below 1 MHz of the reference clock can be appropriately relaxed.

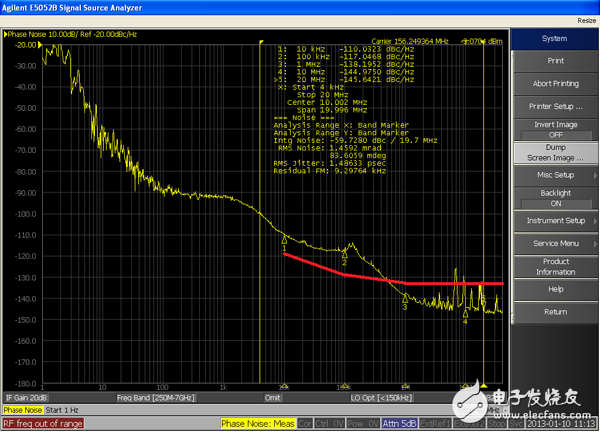

Case 1:

The phase noise of the reference clock does not meet the requirements of the template below 1 MHz, but the noise floor above 1 MHz has a large margin, and a small amount of spurious has a small amount exceeding the standard. This is acceptable, and in engineering practice, it is also successful, fully meeting the user's system requirements.

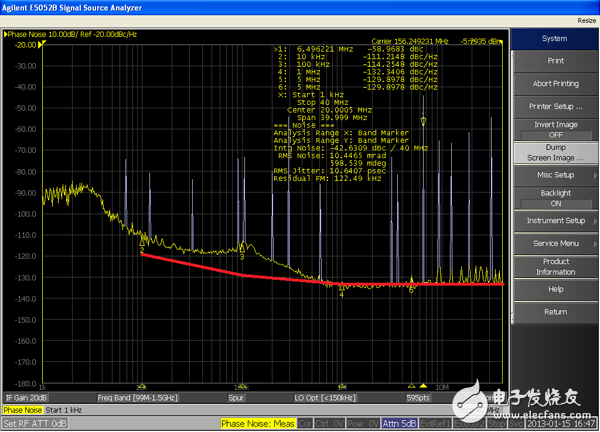

Case 2:

The phase noise of the reference clock does not meet the requirements of the template below 1 MHz, and there is no margin in the noise floor above 1 MHz, and the spurs are seriously exceeded. This is unacceptable, and in engineering practice, it also causes errors in both directions of sending and receiving.

system solar hybrid inverter battery pack,48v lifepo4 battery,lifepo4 battery box,lifepo4 battery solar

Shenzhen Jiesai Electric Co.,Ltd , https://www.gootuenergy.com