1. Verilog realizes basic gate circuit

verilog implements inverter, 2-input AND gate, 2-input OR gate, 2-input NAND gate, 2-input NOR gate, 2-input XOR gate, 2-input XOR gate;

Write simulation programs and perform simulation tests on the realization;

Synthesize and implement the simulated verilog code and download it to basys3 for verification;

2. Verilog implements 2 choices 1MUX

Write simulation program and test it;

Synthesize and implement the simulated verilog code and download it to basys3 for verification;

2.

led[0] sw[0] sw[1] to achieve 2-input AND gate

led[2] sw[2] sw[3] to achieve 2-input OR gate

led[4] sw[4] sw[5] to achieve 2-input NAND gate

led[6] sw[6] sw[7] to achieve 2-input NOR gate

led[8] sw[8] sw[9] to achieve 2-input exclusive OR gate

led[10] sw[10] sw[11] to achieve 2-input XOR gate

led [12] sw [12] to achieve inverter

led[13] sw[13] sw[14] sw[15] to achieve 2 selections 1MUX

3. Implementation module

module fpga001 (

input [15:0] sw,

output ï¼»13:0ï¼½ led

);

assign ledï¼»0] = swï¼»0ï¼½ & swï¼»1ï¼½;

assign ledï¼»2ï¼½ = swï¼»2ï¼½ | swï¼»3ï¼½;

assign ledï¼»4ï¼½ = ~(swï¼»4ï¼½ & swï¼»5ï¼½);

assign ledï¼»6ï¼½ = ~(swï¼»6ï¼½ | swï¼»7ï¼½);

assign ledï¼»8ï¼½ = (swï¼»8ï¼½ & (~swï¼»9ï¼½)) | (~swï¼»8ï¼½ & swï¼»9ï¼½);

assign ledï¼»10ï¼½ = ~((swï¼»10ï¼½ & (~swï¼»11ï¼½)) | (~swï¼»10ï¼½ & swï¼»11ï¼½));

assign ledï¼»12ï¼½ = ~swï¼»12ï¼½;

assign ledï¼»13ï¼½ = ~swï¼»13ï¼½ & swï¼»14ï¼½ | swï¼»13ï¼½ & swï¼»15ï¼½;

endmodule

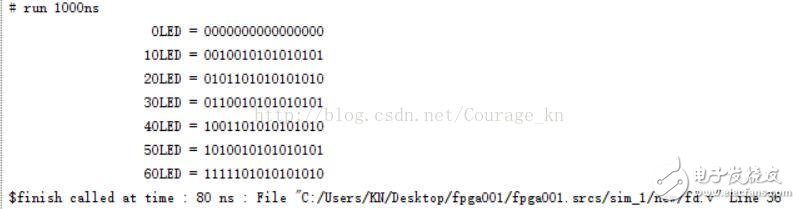

4. Test module

module fd;

reg [15:0] w;

wire [13:0] l;

fpga001 f(w, l);

iniTIal

begin

w = 16'b0;

#10 w = 16'b0010010101010101;

#10 w = 16'b0101101010101010;

#10 w = 16'b0110010101010101;

#10 w = 16'b1001101010101010;

#10 w = 16'b1010010101010101;

#10 w = 16'b1111101010101010;

#20 $finish;

end

iniTIal

begin

$monitor($TIme, "LED = %b", w);

end

endmodule

5. Pin layout

## This file is a general .xdc for the Basys3 rev B board

## To use it in a project:

##-uncomment the lines corresponding to used pins

##-rename the used ports (in each line, after get_ports) according to the top level signal names in the project

## Clock signal

#set_property PACKAGE_PIN W5 ï¼»get_ports clkï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports clkï¼½

#create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports clk]

## Switches

set_property PACKAGE_PIN V17 ï¼»get_ports {swï¼»0ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»0ï¼½}ï¼½

set_property PACKAGE_PIN V16 [get_ports {sw[1]}]

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»1ï¼½}ï¼½

set_property PACKAGE_PIN W16 [get_ports {sw[2]}]

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»2ï¼½}ï¼½

set_property PACKAGE_PIN W17 ï¼»get_ports {swï¼»3ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»3ï¼½}ï¼½

set_property PACKAGE_PIN W15 ï¼»get_ports {swï¼»4ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»4ï¼½}ï¼½

set_property PACKAGE_PIN V15 [get_ports {sw[5]}]

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»5ï¼½}ï¼½

set_property PACKAGE_PIN W14 ï¼»get_ports {swï¼»6ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»6ï¼½}ï¼½

set_property PACKAGE_PIN W13 ï¼»get_ports {swï¼»7ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»7ï¼½}ï¼½

set_property PACKAGE_PIN V2 [get_ports {sw[8]}]

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»8ï¼½}ï¼½

set_property PACKAGE_PIN T3 ï¼»get_ports {swï¼»9ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»9ï¼½}ï¼½

set_property PACKAGE_PIN T2 [get_ports {sw[10]}]

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»10ï¼½}ï¼½

set_property PACKAGE_PIN R3 ï¼»get_ports {swï¼»11ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»11ï¼½}ï¼½

set_property PACKAGE_PIN W2 ï¼»get_ports {swï¼»12ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»12ï¼½}ï¼½

set_property PACKAGE_PIN U1 [get_ports {sw[13]}]

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»13ï¼½}ï¼½

set_property PACKAGE_PIN T1 ï¼»get_ports {swï¼»14ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»14ï¼½}ï¼½

set_property PACKAGE_PIN R2 [get_ports {sw[15]}]

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {swï¼»15ï¼½}ï¼½

## LEDs

set_property PACKAGE_PIN U16 ï¼»get_ports {ledï¼»0ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»0ï¼½}ï¼½

set_property PACKAGE_PIN E19 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»1ï¼½}ï¼½

set_property PACKAGE_PIN U19 ï¼»get_ports {ledï¼»2ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»2ï¼½}ï¼½

set_property PACKAGE_PIN V19 ï¼»get_ports {ledï¼»3ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»3ï¼½}ï¼½

set_property PACKAGE_PIN W18 ï¼»get_ports {ledï¼»4ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»4ï¼½}ï¼½

set_property PACKAGE_PIN U15 ï¼»get_ports {ledï¼»5ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»5ï¼½}ï¼½

set_property PACKAGE_PIN U14 ï¼»get_ports {ledï¼»6ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»6ï¼½}ï¼½

set_property PACKAGE_PIN V14 ï¼»get_ports {ledï¼»7ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»7ï¼½}ï¼½

set_property PACKAGE_PIN V13 ï¼»get_ports {ledï¼»8ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»8ï¼½}ï¼½

set_property PACKAGE_PIN V3 ï¼»get_ports {ledï¼»9ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»9ï¼½}ï¼½

set_property PACKAGE_PIN W3 ï¼»get_ports {ledï¼»10ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»10ï¼½}ï¼½

set_property PACKAGE_PIN U3 ï¼»get_ports {ledï¼»11ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»11ï¼½}ï¼½

set_property PACKAGE_PIN P3 ï¼»get_ports {ledï¼»12ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»12ï¼½}ï¼½

set_property PACKAGE_PIN N3 ï¼»get_ports {ledï¼»13ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»13ï¼½}ï¼½

set_property PACKAGE_PIN P1 [get_ports {led[14]}]

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»14ï¼½}ï¼½

set_property PACKAGE_PIN L1 ï¼»get_ports {ledï¼»15ï¼½}ï¼½

set_property IOSTANDARD LVCMOS33 ï¼»get_ports {ledï¼»15ï¼½}ï¼½

##7 segment display

#set_property PACKAGE_PIN W7 ï¼»get_ports {segï¼»0ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {segï¼»0ï¼½}ï¼½

#set_property PACKAGE_PIN W6 ï¼»get_ports {segï¼»1ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {segï¼»1ï¼½}ï¼½

#set_property PACKAGE_PIN U8 ï¼»get_ports {segï¼»2ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {segï¼»2ï¼½}]

#set_property PACKAGE_PIN V8 ï¼»get_ports {segï¼»3ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {segï¼»3ï¼½}]

#set_property PACKAGE_PIN U5 ï¼»get_ports {segï¼»4ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {segï¼»4ï¼½}]

#set_property PACKAGE_PIN V5 ï¼»get_ports {segï¼»5ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {segï¼»5ï¼½}]

#set_property PACKAGE_PIN U7 ï¼»get_ports {segï¼»6ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {segï¼»6ï¼½}ï¼½

#set_property PACKAGE_PIN V7 ï¼»get_ports dpï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports dpï¼½

#set_property PACKAGE_PIN U2 ï¼»get_ports {anï¼»0ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {anï¼»0ï¼½}ï¼½

#set_property PACKAGE_PIN U4 ï¼»get_ports {anï¼»1ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {anï¼»1ï¼½}ï¼½

#set_property PACKAGE_PIN V4 ï¼»get_ports {anï¼»2ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {anï¼»2ï¼½}]

#set_property PACKAGE_PIN W4 ï¼»get_ports {anï¼»3ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {anï¼»3ï¼½}]

##Buttons

#set_property PACKAGE_PIN U18 ï¼»get_ports btnCï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports btnCï¼½

#set_property PACKAGE_PIN T18 ï¼»get_ports btnUï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports btnUï¼½

#set_property PACKAGE_PIN W19 ï¼»get_ports btnLï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports btnLï¼½

#set_property PACKAGE_PIN T17 ï¼»get_ports btnRï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports btnRï¼½

#set_property PACKAGE_PIN U17 ï¼»get_ports btnDï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports btnDï¼½

##Pmod Header JA

##Sch name = JA1

#set_property PACKAGE_PIN J1 ï¼»get_ports {JAï¼»0ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JAï¼»0ï¼½}]

##Sch name = JA2

#set_property PACKAGE_PIN L2 ï¼»get_ports {JAï¼»1ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JAï¼»1ï¼½}]

##Sch name = JA3

#set_property PACKAGE_PIN J2 ï¼»get_ports {JAï¼»2ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JAï¼»2ï¼½}]

##Sch name = JA4

#set_property PACKAGE_PIN G2 ï¼»get_ports {JAï¼»3ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JAï¼»3ï¼½}]

##Sch name = JA7

#set_property PACKAGE_PIN H1 ï¼»get_ports {JAï¼»4ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JAï¼»4ï¼½}]

##Sch name = JA8

#set_property PACKAGE_PIN K2 ï¼»get_ports {JAï¼»5ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JAï¼»5ï¼½}]

##Sch name = JA9

#set_property PACKAGE_PIN H2 ï¼»get_ports {JAï¼»6ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JAï¼»6ï¼½}]

##Sch name = JA10

#set_property PACKAGE_PIN G3 ï¼»get_ports {JAï¼»7ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JAï¼»7ï¼½}]

##Pmod Header JB

##Sch name = JB1

#set_property PACKAGE_PIN A14 ï¼»get_ports {JBï¼»0ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JBï¼»0ï¼½}]

##Sch name = JB2

#set_property PACKAGE_PIN A16 ï¼»get_ports {JBï¼»1ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JBï¼»1ï¼½}ï¼½

##Sch name = JB3

#set_property PACKAGE_PIN B15 ï¼»get_ports {JBï¼»2ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JBï¼»2ï¼½}ï¼½

##Sch name = JB4

#set_property PACKAGE_PIN B16 ï¼»get_ports {JBï¼»3ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JBï¼»3ï¼½}]

##Sch name = JB7

#set_property PACKAGE_PIN A15 ï¼»get_ports {JBï¼»4ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JBï¼»4ï¼½}]

##Sch name = JB8

#set_property PACKAGE_PIN A17 ï¼»get_ports {JBï¼»5ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JBï¼»5ï¼½}]

##Sch name = JB9

#set_property PACKAGE_PIN C15 ï¼»get_ports {JBï¼»6ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JBï¼»6ï¼½}ï¼½

##Sch name = JB10

#set_property PACKAGE_PIN C16 ï¼»get_ports {JBï¼»7ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JBï¼»7ï¼½}]

##Pmod Header JC

##Sch name = JC1

#set_property PACKAGE_PIN K17 ï¼»get_ports {JCï¼»0ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JCï¼»0ï¼½}ï¼½

##Sch name = JC2

#set_property PACKAGE_PIN M18 ï¼»get_ports {JCï¼»1ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JCï¼»1ï¼½}ï¼½

##Sch name = JC3

#set_property PACKAGE_PIN N17 ï¼»get_ports {JCï¼»2ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JCï¼»2ï¼½}ï¼½

##Sch name = JC4

#set_property PACKAGE_PIN P18 ï¼»get_ports {JCï¼»3ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JCï¼»3ï¼½}]

##Sch name = JC7

#set_property PACKAGE_PIN L17 ï¼»get_ports {JCï¼»4ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JCï¼»4ï¼½}]

##Sch name = JC8

#set_property PACKAGE_PIN M19 ï¼»get_ports {JCï¼»5ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JCï¼»5ï¼½}]

##Sch name = JC9

#set_property PACKAGE_PIN P17 ï¼»get_ports {JCï¼»6ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JCï¼»6ï¼½}ï¼½

##Sch name = JC10

#set_property PACKAGE_PIN R18 ï¼»get_ports {JCï¼»7ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JCï¼»7ï¼½}]

##Pmod Header JXADC

##Sch name = XA1_P

#set_property PACKAGE_PIN J3 ï¼»get_ports {JXADCï¼»0ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JXADCï¼»0ï¼½}ï¼½

##Sch name = XA2_P

#set_property PACKAGE_PIN L3 ï¼»get_ports {JXADCï¼»1ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JXADCï¼»1ï¼½}]

##Sch name = XA3_P

#set_property PACKAGE_PIN M2 ï¼»get_ports {JXADCï¼»2ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JXADCï¼»2ï¼½}]

##Sch name = XA4_P

#set_property PACKAGE_PIN N2 ï¼»get_ports {JXADCï¼»3ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JXADCï¼»3ï¼½}]

##Sch name = XA1_N

#set_property PACKAGE_PIN K3 ï¼»get_ports {JXADCï¼»4ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JXADCï¼»4ï¼½}]

##Sch name = XA2_N

#set_property PACKAGE_PIN M3 ï¼»get_ports {JXADCï¼»5ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JXADCï¼»5ï¼½}]

##Sch name = XA3_N

#set_property PACKAGE_PIN M1 ï¼»get_ports {JXADCï¼»6ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JXADCï¼»6ï¼½}ï¼½

##Sch name = XA4_N

#set_property PACKAGE_PIN N1 ï¼»get_ports {JXADCï¼»7ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {JXADCï¼»7ï¼½}]

##VGA Connector

#set_property PACKAGE_PIN G19 ï¼»get_ports {vgaRedï¼»0ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {vgaRedï¼»0ï¼½}ï¼½

#set_property PACKAGE_PIN H19 ï¼»get_ports {vgaRedï¼»1ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {vgaRedï¼»1ï¼½}ï¼½

#set_property PACKAGE_PIN J19 ï¼»get_ports {vgaRedï¼»2ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {vgaRedï¼»2ï¼½}ï¼½

#set_property PACKAGE_PIN N19 ï¼»get_ports {vgaRedï¼»3ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {vgaRedï¼»3ï¼½}]

#set_property PACKAGE_PIN N18 ï¼»get_ports {vgaBlueï¼»0ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {vgaBlueï¼»0ï¼½}ï¼½

#set_property PACKAGE_PIN L18 ï¼»get_ports {vgaBlueï¼»1ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {vgaBlueï¼»1ï¼½}]

#set_property PACKAGE_PIN K18 ï¼»get_ports {vgaBlueï¼»2ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {vgaBlueï¼»2ï¼½}]

#set_property PACKAGE_PIN J18 ï¼»get_ports {vgaBlueï¼»3ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {vgaBlueï¼»3ï¼½}]

#set_property PACKAGE_PIN J17 ï¼»get_ports {vgaGreenï¼»0ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {vgaGreenï¼»0ï¼½}]

#set_property PACKAGE_PIN H17 ï¼»get_ports {vgaGreenï¼»1ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {vgaGreenï¼»1ï¼½}]

#set_property PACKAGE_PIN G17 ï¼»get_ports {vgaGreenï¼»2ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {vgaGreenï¼»2ï¼½}]

#set_property PACKAGE_PIN D17 ï¼»get_ports {vgaGreenï¼»3ï¼½}]

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {vgaGreenï¼»3ï¼½}]

#set_property PACKAGE_PIN P19 ï¼»get_ports Hsyncï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports Hsyncï¼½

#set_property PACKAGE_PIN R19 ï¼»get_ports Vsyncï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports Vsyncï¼½

##USB-RS232 Interface

#set_property PACKAGE_PIN B18 ï¼»get_ports RsRxï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports RsRxï¼½

#set_property PACKAGE_PIN A18 ï¼»get_ports RsTxï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports RsTxï¼½

##USB HID (PS/2)

#set_property PACKAGE_PIN C17 ï¼»get_ports PS2Clkï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports PS2Clkï¼½

#set_property PULLUP true ï¼»get_ports PS2Clkï¼½

#set_property PACKAGE_PIN B17 ï¼»get_ports PS2Dataï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports PS2Dataï¼½

#set_property PULLUP true ï¼»get_ports PS2Dataï¼½

##Quad SPI Flash

##Note that CCLK_0 cannot be placed in 7 series devices. You can access it using the

##STARTUPE2 primiTIve.

#set_property PACKAGE_PIN D18 ï¼»get_ports {QspiDBï¼»0ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {QspiDBï¼»0ï¼½}ï¼½

#set_property PACKAGE_PIN D19 ï¼»get_ports {QspiDBï¼»1ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {QspiDBï¼»1ï¼½}ï¼½

#set_property PACKAGE_PIN G18 ï¼»get_ports {QspiDBï¼»2ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {QspiDBï¼»2ï¼½}ï¼½

#set_property PACKAGE_PIN F18 ï¼»get_ports {QspiDBï¼»3ï¼½}ï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports {QspiDBï¼»3ï¼½}ï¼½

#set_property PACKAGE_PIN K19 ï¼»get_ports QspiCSnï¼½

#set_property IOSTANDARD LVCMOS33 ï¼»get_ports QspiCSnï¼½

Ceramic Guides,Ceramic Eyelet Guide,Ceramic Eyelet Guides,Eramic Eyelet Guide

Yixing Guangming Special Ceramics Co.,Ltd , https://www.yxgmtc.com